Weak-Micro Viaを解決する無電解銅めっきプロセス

OPC FLETプロセス

近年、電子機器の小型化・高性能化・高機能化によって、半導体パッケージ基板(ICサブストレート)には、さらなる配線の微細化とマイクロビアの小径化が求められています。 これまで半導体パッケージ基板のビア径は80µm程度が一般的でしたが、近年、50µmに迫る小径ビアが採用されるようになりました。 今後、さらにビアが小径化すると、ビアと内層銅の接続面積が著しく狭小化し、内層銅と無電解銅めっきの界面の接続信頼性悪化の懸念がクローズアップされてきます。

そこで、当社は次世代半導体パッケージ基板向けに、接続信頼性向上に貢献する無電解銅めっきプロセス「OPC FLETプロセス」を新たに開発しました。

特長・仕様

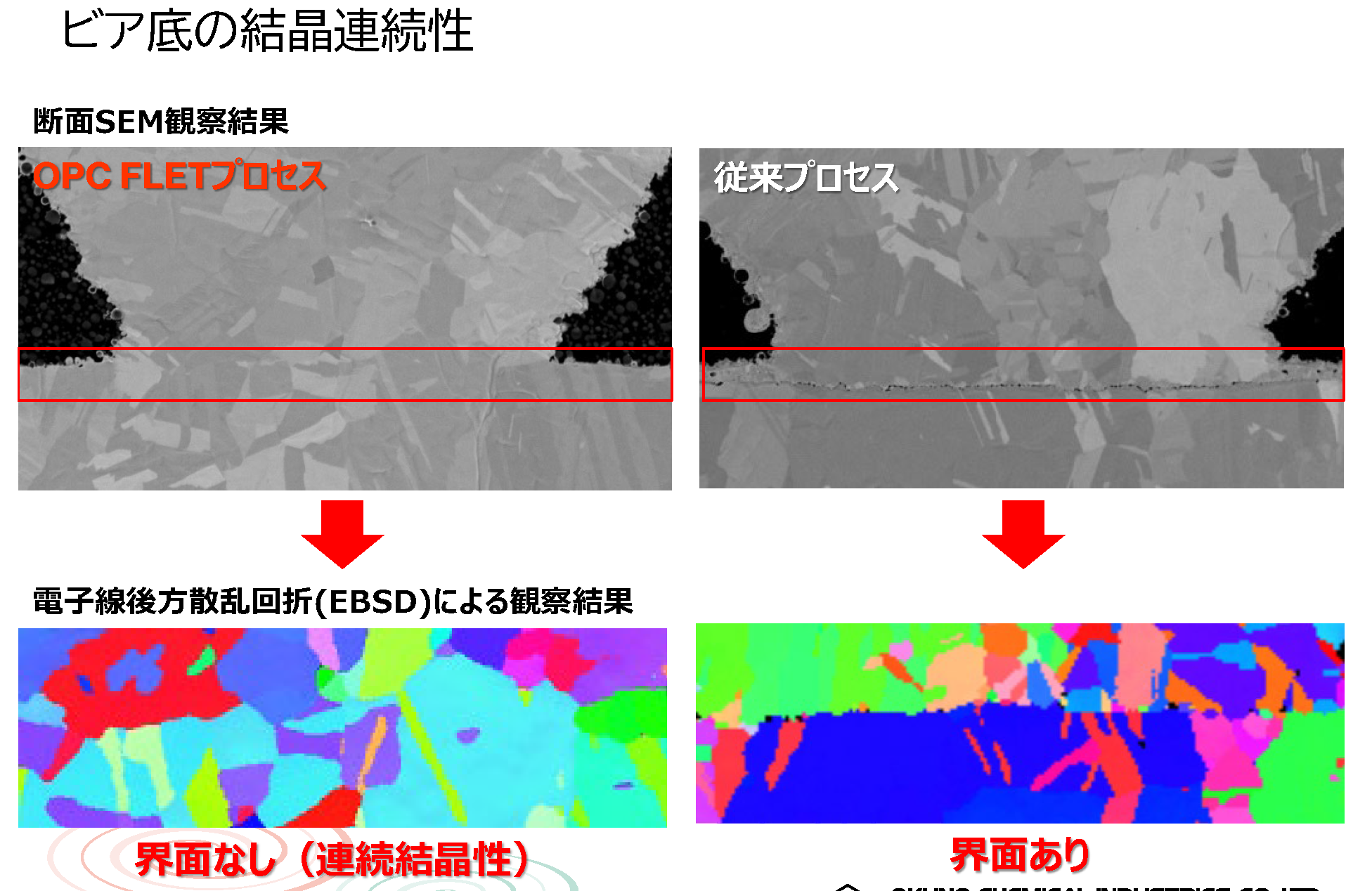

従来の無電解銅めっきプロセスの場合、後工程の電気銅めっき皮膜と内層銅界面に無電解銅めっき層が介在し、かつ、無電解銅めっきと内層銅の界面に多数のナノボイドが発生して、接続信頼性を損なうという課題がありました。

当社の新しい無電解銅めっきプロセス「OPC FLETプロセス」は、触媒化プロセスを最適化、無電解銅めっき皮膜を薄膜化、高純度化しました。 それらによって、後工程の電気銅めっき皮膜の再結晶化の過程で、銅めっき皮膜と内層銅の結晶が一体化して結晶の連続性が実現し、さらに、内層銅との界面で発生するナノボイドの発生を大きく抑制します。

さらに、無電解銅めっきの低膜厚化が、フラッシュエッチング時の銅の溶解量を減少させ、セミアディティブ法による微細回路形成を容易にします。 本プロセスは、マイクロビアと内層銅間が断裂することによって生じるWeak-Micro Via問題(初期および経時の故障)の解決に貢献します。

Weak-Micro Viaを解決する無電解銅めっきプロセス

マイクロビアと内層銅間が断裂することによって生じるWeak-Micro Via問題(初期および経時の故障)の解決に貢献します。